- HT77221 HT77211 4.0V~30V输入,2A/1.2A同步降压变换器

- NS4117X 系列 外置 MOS 管开关降压型 LED 恒流控制器

- HT71663 13V,12A全集成同步升压转换器

- HT71763 20V,15A全集成同步升压转换器

- NS2160 同步开关型降压锂电池充电管理 IC

- HT7702 2.5~5.5V输入,2A同步降压变换器

- HT77231 4.0V~28V输入,3.5A同步降压变换器

- AT2401C 射频2.4GHzPA发射接收芯片

- HT3166 免电感滤波2×30W AB/D类音频功放

- HT81298 内置升压的10W立体声D类音频功放

- HT71778 实时音频信号跟踪的18V, 15A全集成同

- HT97226 160mW免输出耦合电容的立体声耳机放大器

- HT71782 20v 15a 同步升压芯片

- HT78621 60V输入,3.5A开关限流降压变换器

运算放大器输入偏置电流的理解和影响

【模拟电路设计】输入偏置电流(Input Bias Current, IB)

对于新手或者从事芯片封装行业的人员经常拿到运放的技术手册不会看,我们最近就以LM741 Operational Amplifier来进行讲解,首先先看看图1,里面涉及很多参数,也是挑选运放最重要的指标,而前面已经讲述了Input Offset Voltage(输入失调电压)和Slew Rate(压摆率),大概知道了他们的作用,对他们已经有了一个大概的认识,那今天我们主要讲解的内容就是Input Bias Current(输入偏置电流)。

图1 LM741 Electrical Characteristics

01输入偏置电流的理解

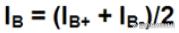

理论来说输入应具有无穷大的阻抗,这意味着绝对没有电流流入其中。然而,事实并非如此,所有运算放大器都会有电流流入。流过运算放大器输入端的电流量称为输入偏置电流。输入偏置电流就是当运放的输出直流电压为零时运放两输入端流进或流出直流电流的平均值。将输入偏置电流指定为同相端输入偏置电流IB+和反相端输入偏置电流IB的平均值,如图2所示。

图2 偏置电流就是两输入端之和的平均值

输入偏置电流与制造工艺有关系,CMOS和JFET输入比标准双极输入有低得多的输入电流。

输入偏置电流会在输入端产生额外的失调电压降,从而导致输出端出现失调误差。对于大多数产品,此问题可以忽略不计,但在某些情况下需要重点考虑。当源阻抗较高时,需要关注输入偏置电流。如果运算放大器具有高输入偏置电流,它会加载源并且会看到低于预期的电压。如果源阻抗很高,最好的解决方案是使用带有CMOS或JFET 输入的运算放大器。还可以通过使用缓冲级来驱动具有高输入偏置电流的运算放大器来降低源阻抗。在双极输入的情况下,可以通过匹配输入端的阻抗来消除失调电流。对于CMOS或JFET 输入,偏移电流通常不是问题,也不需要匹配阻抗。

CMOS放大器的输入偏置电流主要由ESD结构、保护二极管和连接到输入的其他次级电路的泄漏电流决定。该泄漏电流的幅度很小——大约为皮安(pA),如图3所示

图3 输入级显示了泄漏如何充当输入偏置电流

而双极结型晶体管 (BJT) 放大器的输入需要基极电流以实现适当的偏置,因此 BJT 输入偏置电流要大得多——大约为微安(µA)或纳安(nA)。对于双极运算放大器,当输入差分晶体管导通时,少量电流在基极和发射极之间流动。换句话说,基极-发射极电流是偏置晶体管所需的电流量。该电流通常在纳安或微安的范围内。对于PNP输入对,电流流出输入晶体管,如图4所示为双极放大器的简化PNP输入级。对于轨到轨输入双极运算放大器,将使用额外的NPN输入对,电流将流入NPN输入级。因此,输入偏置电流是BJT放大器的一个重要问题。

图4 输入偏置电流如何改变放大器输出

问题1:那么你可能会有疑惑,既然CMOS放大器的输入偏置电流几乎可以忽略不计,为什么还需要BJT放大器?

回答1:在相同的静态电流下,与CMOS晶体管相比,BJT具有更大的跨导(gm)。此外,BJT 之间的匹配也好很多,1/f噪声也是如此。这三个优点对于高速精密放大器都是至关重要的;因此,BJT 输入在高性能运算放大器和全差分放大器(FDA)中无处不在。

02输入偏置电流的影响

输入偏置电流会影响放大器的输出。例如,如果有一个大电阻与运算放大器输入串联,则IB流过它并增加一个偏移量。例如,图5中所示的原理图。IB =10nA的电压跟随器电路(也称为单位增益缓冲电路)中的1MΩ输入电阻器会在电阻器上产生额外的10mV电压降,从而导致10mV的输出误差。

图5 输入偏置电流在该单位增益电路中产生电压偏移

为了消除IB产生的任何偏移电压,有时电路设计人员会尝试匹配运算放大器的同相和反相输入端子所见的输入电阻,如图6所示。然而,如果偏置电流不匹配,产生的输入失调电流(IOS)仍会产生额外的输入失调电压。IOS产生的这种偏移电压会导致输出误差。

图6 输入电阻匹配可以降低输入偏置电流的影响

上一篇:一文讲解ADC模数转换芯片的原理及转换过程

下一篇:MOSFET的结构和电路符号